บทความ

19

Jan

การเรียนรู้เกี่ยวกับแอมปลิฟายเออร์ขั้วเดียว

แอมปลิฟายเออร์ขั้วเดียวและการเรียงตัวสำหรับสัญญาณ AC ในการออกแบบแอมปลิฟายเออร์โดยเน้นความมั่นคงของจุด Q.

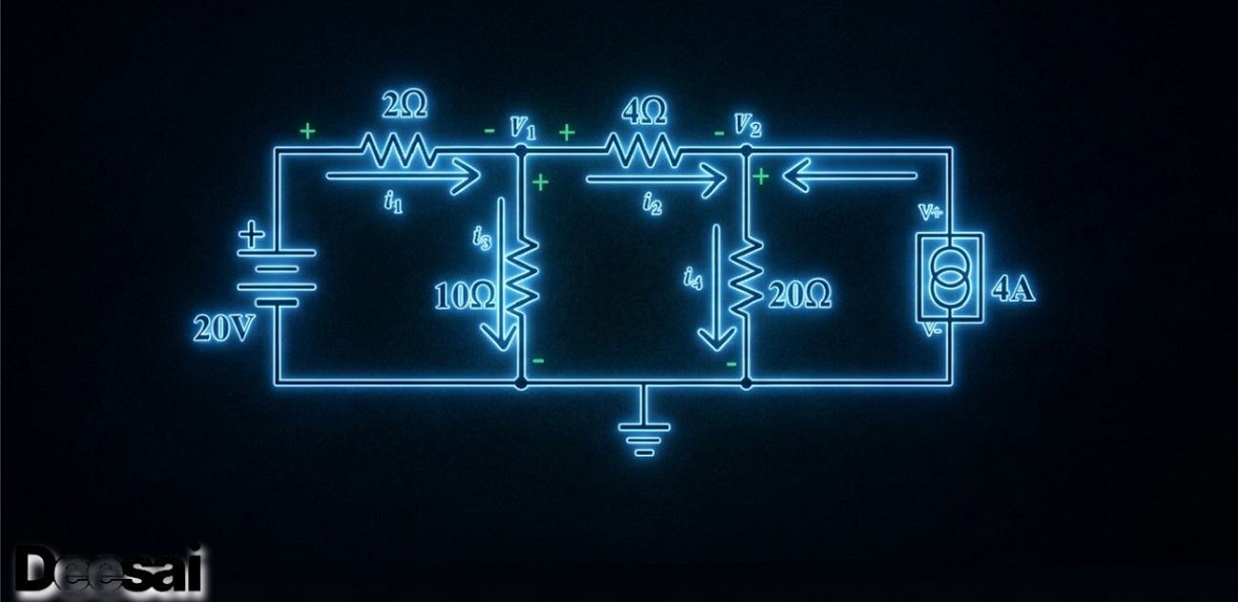

เพื่อขยายสัญญาณเข้า AC ที่สลับระหว่างค่าบวกและค่าลบ คุณต้องตั้งค่าวงจรครอบนิวต์ขั้วส่วนกลาง (common emitter amplifier circuit) วงจรนี้ช่วยให้ทรานซิสเตอร์สามารถทำงานในช่วงค่าที่สูงเหล่านี้ได้ โดยการทำงานนี้เป็นการปรับแต่งที่รู้จักกันเรียกว่า biasing (การตั้งค่า)

Biasing มีความสำคัญมากในการออกแบบแอมปลิฟายเออร์ เพราะมันจะกำหนดจุดทำงานที่ถูกต้องสำหรับแอมปลิฟายเออร์แบบทรานซิสเตอร์ ทำให้เตรียมพร้อมรับสัญญาณและลดการสะเทือนในสัญญาณเอาท์พุทได้อย่างมีประสิทธิภาพ

เส้นลอดไฟฟ้าสถิตหรือ DC load line ที่วาดบนกราฟแสดงสถานะเอาท์พุทของแอมปลิฟายเออร์จะแสดงจุดทำงานที่เป็นไปได้ของทรานซิสเตอร์ ตั้งแต่เต็ม "ON" ไปจนถึงเต็ม "OFF" มันยังช่วยในการกำหนดจุดทำงานที่มั่นคงหรือ Q-point ของแอมปลิฟายเออร์

วัตถุประสงค์หลักของแอมปลิฟายเออร์สัญญาณขนาดเล็กคือขยายสัญญาณนำเข้าด้วยการสะเทือนน้อยในสัญญาณเอาท์พุท โดยพื้นฐานแล้วเป็นการสร้างเวอร์ชันขนาดใหญ่ของสัญญาณนำเข้า

เพื่อลดการสะเทือนในสัญญาณน้อยลง ซึ่งเป็นจุด DC ในการทำงานของแอมปลิฟายเออร์ จุดนี้สามารถกำหนดได้ที่ใดก็ได้บนเส้นลอดไฟฟ้าโดยใช้การเรียงตัว biasing ที่เหมาะสม ตำแหน่งที่เหมาะสมสำหรับจุด Q นี้คือใกล้กับศูนย์ของเส้นลอดไฟฟ้าเท่าที่เป็นไปได้ ทำให้เกิดการทำงานของแอมปลิฟายเออร์แบบ A (คือ Vce = 1/2Vcc)

ตอนนี้เรามาพิจารณาแอมป์ปลิฟายเออร์ที่ใช้ตั้งค่าวงจรครอบนิวต์ขั้วส่วนกลาง (Common Emitter Amplifier) ตามด้านล่าง

แอมป์ปลิฟายเออร์ที่ใช้ตั้งค่าวงจรครอบนิวต์ขั้วส่วนกลาง (Common Emitter Amplifier):

แอมป์ปลิฟายเออร์ที่ใช้ตั้งค่าวงจรครอบนิวต์ขั้วส่วนกลางที่แสดงข้างต้นใช้เทคนิคที่เรียกว่า "Voltage Divider Biasing" ในการเรียงตัวนี้เป็นวิธีที่ใช้บ่อยในการออกแบบวงจรแอมปลิฟายเออร์สัญญาณไบโพลาร์ทรานซิสเตอร์ โดยที่ตัววงจรจะเป็นเส้นตรงที่มีตัวต้านทานสองตัว เมื่อเรียงตัวเหล่านี้แล้วจะเกิดเครือข่ายการแบ่งแรงดันข้ามแหล่งจ่ายไฟฟ้า ทำให้จุดกึ่งกลางให้แรงดันขาเบสที่จำเป็นให้กับทรานซิสเตอร์เพื่อการทำงาน

การเรียงตัวด้วยวิธีนี้ช่วยลดผลกระทบจากการเปลี่ยนแปลงของค่า Beta (β) โดยรักษาระดับแรงดันขาเบสให้คงที่ ซึ่งทำให้วงจรมีความเสถียรและมั่นคงมากยิ่งขึ้นได้

แรงดันฐาน (Vb) ที่เงื่อนไขถูกกำหนดโดยเครือข่าย potential divider สามารถคำนวณได้โดยใช้สูตรตัวหารแรงดัน (Voltage Divider Formula) ที่เกี่ยวข้องกับแรงดันจ่ายไฟฟ้า (Vcc) และค่าความต้านทานรวม (RT) ของตัวต้านทาน R1 และ R2 ซึ่งมีสัมพันธ์กับแรงดันที่ตัดกันระหว่างตัวต้านทาน R1 และ R2 ที่ทำให้แรงดันฐาน (Vb) มีค่าที่ต่ำกว่าแรงดันจ่ายไฟ

เครือข่าย potential divider ในวงจรขยาย common emitter ทำหน้าที่แบ่งแรงดันจ่ายไฟฟ้าให้สัมพันธ์กันตามค่าความต้านทาน คุณสามารถคำนวณหาแรงดันอ้างอิง bias นี้ได้โดยใช้สูตรตัวหารแรงดันที่เรียกว่า voltage divider formula:

Voltage Divider Formula

แรงดันจ่ายไฟฟ้า (Vcc) เป็นตัวกำหนดกระแสคอลเล็กเตอร์สูงสุด (Ic_max) เมื่อทรานซิสเตอร์อยู่ในสถานะ saturation โดยมี Vce = 0 กระแสฐาน (Ib) สำหรับทรานซิสเตอร์สามารถคำนวณได้จากกระแสคอลเล็กเตอร์ (Ic) และค่ากำไรกระแส DC ที่ชื่อว่า Beta (β) ของทรานซิสเตอร์

Beta Value

Beta ที่แสดงด้วยตัวอักษร hFE ในข้อมูลชีท แสดงอัตราส่วนระหว่างกระแสที่ไหลผ่านผู้ปรับปรุง (Ic) และกระแสฐาน (Ib) ในทรานซิสเตอร์แบบ common emitter นั่นหมายความว่า Beta เป็นตัวบอกว่าแรงกระแสฐานที่ไหลผ่านทรานซิสเตอร์จะมีผลต่อแรงกระแสผ่านทรานซิสเตอร์ในอัตราใด การเปลี่ยนแปลงขนาดค่ากระแสฐานสามารถทำให้ค่ากระแสผ่านทรานซิสเตอร์เปลี่ยนแปลงได้อย่างมาก

หนึ่งข้อสำคัญเกี่ยวกับ Beta: ทรานซิสเตอร์ที่มีชนิดและเลขชิ้นงานเดียวกันอาจแสดงค่า Beta ที่แตกต่างกันได้มาก ตัวอย่างเช่น ทรานซิสเตอร์บิปอาร์ BC107 NPN มีค่ากำไรกระแสดีซี DC (DC current gain) ที่อยู่ในช่วงค่า Beta ตั้งแต่ 110 ถึง 450 (ตามข้อมูลชีท) ความแตกต่างนี้มาจากความหลากหลายในกระบวนการผลิตของทรานซิสเตอร์ซึ่งอาจไม่สามารถควบคุมได้อย่างแม่นยำ ทำให้ค่า Beta ของแต่ละชิ้นของทรานซิสเตอร์ในชนิดเดียวกันอาจแตกต่างกันได้

เมื่อตัวต้านทานฐานหรือตัวกลางได้รับแรงดันที่ส่งผ่านไป (forward-biased) แรงดันนำไฟฟ้า (Ve) จะต่าง โดยการการลดค่าแรงดันของอุปกรณ์ที่เชื่อมต่อกับแรงดันฐาน การรับรู้แรงดันที่ข้ามตัวต้านทานทำให้สามารถคำนวณหาค่ากระแสนำไฟฟ้า (Ie) ได้โดยใช้กฎของโอห์ม และสามารถประมาณค่ากระแสคอลเล็กเตอร์ (Ic) โดยทั่วไปมันจะเท่ากับค่ากระแสนำไฟฟ้า

บทความ

January 26, 2024

การเรียนรู้เกี่ยวกับแอมปลิฟายเออร์ขั้วเดียว

แอมปลิฟายเออร์ขั้วเดียวและการเรียงตัวสำหรับสัญญาณ AC ในการออกแบบแอมปลิฟายเออร์โดยเน้นความมั่นคงของจุด Q.

by

นักเขียนบทความ