ผลิตภัณฑ์

19

Jan

การใช้งาน Pipelining ในการออกแบบ IC ดิจิทัล: เพิ่มประสิทธิภาพและการไหลของข้อมูล

วิธีการใช้งาน Pipelining ในวงจรดิจิทัลเพื่อเพิ่มความเร็วในการประมวลผลข้อมูลโดยไม่ต้องเพิ่มความเร็วสัญญาณนาฬิกา

การใช้ Pipelining ในการออกแบบ IC ดิจิทัลเป็นวิธีที่มีประสิทธิภาพในการเพิ่มอัตราการประมวลผลข้อมูล เทคนิคนี้แบ่งการทำงานที่ซับซ้อนออกเป็นหลายขั้นตอน ซึ่งแต่ละขั้นตอนจะดำเนินการเป็นลำดับโดยส่วนต่าง ๆ ของวงจร แตกต่างจากการเพิ่มความเร็วของสัญญาณนาฬิกา Pipelining ช่วยเพิ่มอัตราการประมวลผลโดยไม่ต้องเพิ่มความถี่ในการทำงาน ช่วยรักษาเสถียรภาพของระบบและเพิ่มประสิทธิภาพ

ในการออกแบบวงจรดิจิทัล แต่ละขั้นของ Pipeline จะทำเพียงส่วนหนึ่งของงานโดยรวม ข้อมูลจะเคลื่อนจากขั้นตอนหนึ่งไปยังอีกขั้นหนึ่งในแต่ละรอบของสัญญาณนาฬิกา ซึ่งหมายความว่าหลายกระบวนการสามารถดำเนินไปพร้อมกันในแต่ละขั้นตอนได้ ทำให้ประสิทธิภาพดีขึ้นอย่างมาก เนื่องจากคำสั่งหลาย ๆ ชุดสามารถถูกประมวลผลในเฟสที่ซ้อนทับกัน แทนที่จะรอให้คำสั่งเสร็จสมบูรณ์ก่อนจึงจะเริ่มคำสั่งถัดไปได้

ในการใช้ Pipelining นักออกแบบจะทำการแบ่งกระบวนการออกเป็นงานย่อย ๆ ที่จัดการได้ง่ายและกำหนดให้กับแต่ละส่วนของวงจร โดยแต่ละส่วนจะทำงานเฉพาะในส่วนหนึ่งของคำสั่ง เช่น การดึงข้อมูล การถอดรหัส การดำเนินการ หรือการจัดเก็บข้อมูล การแบ่งงานเช่นนี้ช่วยลดภาระของแต่ละส่วน และป้องกันความล่าช้าที่อาจเกิดจากขั้นตอนที่ซับซ้อนเกินไปเพียงขั้นตอนเดียว

หนึ่งในความท้าทายของการใช้ Pipelining คือการจัดการการพึ่งพาข้อมูล เมื่อคำสั่งหนึ่งต้องการผลลัพธ์ของคำสั่งก่อนหน้าที่ยังอยู่ระหว่างการดำเนินการ จะทำให้เกิดความล่าช้า ปัญหานี้เรียกว่า Data Hazard ซึ่งสามารถแก้ไขได้ด้วยเทคนิคเช่น Forwarding และ Stalling โดย Forwarding จะถ่ายโอนข้อมูลที่จำเป็นจากขั้นตอนหนึ่งไปยังอีกขั้นตอนหนึ่งโดยตรงเพื่อข้ามความล่าช้า ส่วน Stalling จะหยุดการเคลื่อนของ Pipeline ชั่วคราวจนกว่าการพึ่งพาจะได้รับการแก้ไข

Control Hazard ก็เป็นอีกปัญหาที่เกิดขึ้นเมื่อมีคำสั่งสาขา ซึ่งอาจทำให้ Pipeline ดึงข้อมูลที่ไม่ถูกต้องหากเส้นทางสาขายังไม่แน่นอน เทคนิคการทำนายสาขา หรือ Branch Prediction ช่วยแก้ปัญหานี้โดยการคาดเดาเส้นทางที่คำสั่งจะตามไป ซึ่งจะช่วยลดการขัดจังหวะใน Pipeline แม้ว่าจะมีการทำนายผิดบ้างเป็นบางครั้ง แต่วิธีนี้ยังคงช่วยเพิ่มประสิทธิภาพโดยรวม

นอกจากนี้ Clock Skew ซึ่งเป็นความคลาดเคลื่อนเล็กน้อยในสัญญาณนาฬิการะหว่างขั้นตอนของ Pipeline ก็เป็นอีกหนึ่งความท้าทาย นักออกแบบใช้กลยุทธ์การกระจายสัญญาณนาฬิกาเพื่อซิงโครไนซ์สัญญาณระหว่างขั้นตอนต่าง ๆ เพื่อลดความคลาดเคลื่อนเหล่านี้ให้มากที่สุด การรักษาให้มี Skew ต่ำที่สุดเป็นสิ่งสำคัญในแอปพลิเคชันที่ทำงานที่ความถี่สูง ซึ่งแม้แต่ความล่าช้าเล็กน้อยก็อาจส่งผลต่ออัตราการประมวลผลโดยรวมได้

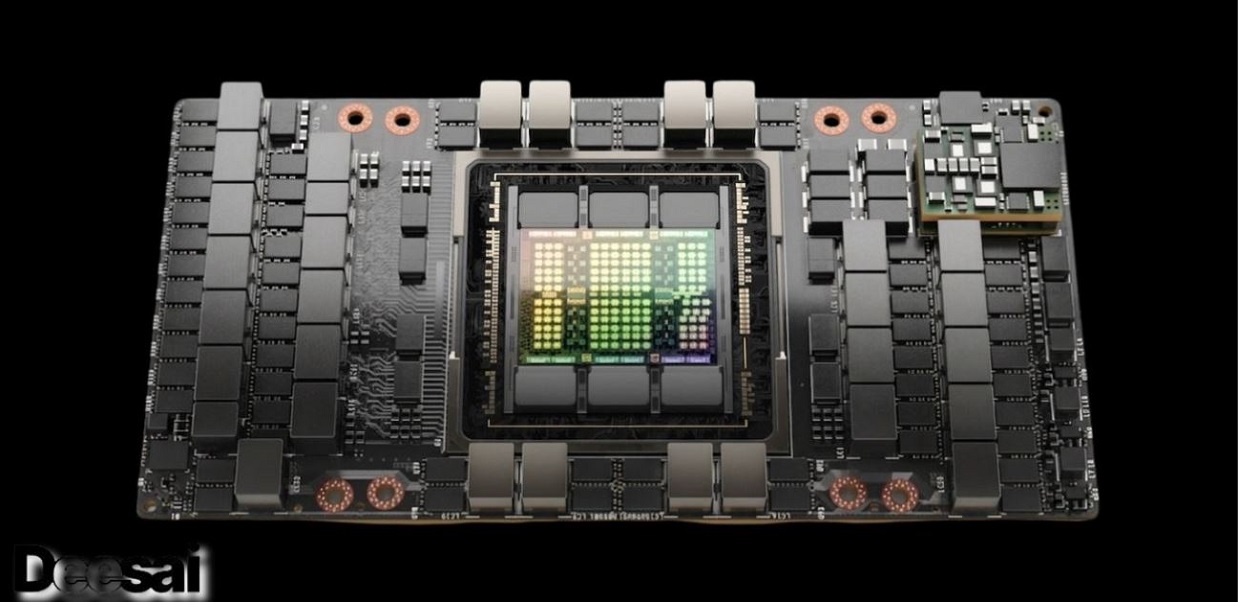

IC ดิจิทัลที่ออกแบบด้วย Pipelining โดดเด่นในแอปพลิเคชันที่ต้องการการประมวลผลข้อมูลอย่างรวดเร็ว เช่น การประมวลผลสัญญาณและการเรนเดอร์กราฟิก วิธีการ Pipeline ช่วยให้วงจรเหล่านี้สามารถจัดการกับปริมาณข้อมูลขนาดใหญ่ที่ความเร็วสูงได้ ทำให้เป็นส่วนสำคัญในอุปกรณ์ที่ต้องการความสามารถในการประมวลผลแบบเรียลไทม์

สรุป Pipelining เป็นเทคนิคที่ทรงพลังในการเพิ่มประสิทธิภาพของ IC ดิจิทัล ด้วยการแบ่งงานออกเป็นขั้นตอนต่าง ๆ ทำให้สามารถประมวลผลคำสั่งหลายคำสั่งได้พร้อมกัน แม้ว่าจะมีความท้าทายเช่น Data Hazard และ Control Hazard แต่กลยุทธ์ Pipelining ที่มีประสิทธิภาพช่วยให้อัตราการประมวลผลสูงขึ้นและเพิ่มประสิทธิภาพโดยไม่ต้องเผชิญปัญหาจากการเพิ่มความเร็วของสัญญาณนาฬิกา การออกแบบและการปรับแต่งอย่างรอบคอบทำให้ Pipelining ยังคงเป็นแกนหลักของการออกแบบวงจรดิจิทัลสมัยใหม่ ขยายขอบเขตของพลังการประมวลผลในอุปกรณ์อิเล็กทรอนิกส์

ผลิตภัณฑ์

November 14, 2024

การใช้งาน Pipelining ในการออกแบบ IC ดิจิทัล: เพิ่มประสิทธิภาพและการไหลของข้อมูล

วิธีการใช้งาน Pipelining ในวงจรดิจิทัลเพื่อเพิ่มความเร็วในการประมวลผลข้อมูลโดยไม่ต้องเพิ่มความเร็วสัญญาณนาฬิกา

by

นักเขียนบทความ